G40 Assy Ph.6-2 PC RX/TX control. [G40]

G40 Assy Phase 6 の Testing で詰まっています。

外部からの SW 接続で動作 Test をすると Step 1 はOK ですが、Step 2 が正しく動作しません。

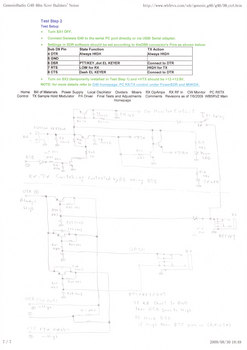

そこで回路図を追ってみました。

この回路をみると上側の回路で PC からの RTS 信号で受信動作から送信動作に回路の電源を切り変えています。 ここはテスト的に繋いだ SX1 で On/Off が確認できています。

次に下側の回路で DTR からの信号を電源として、K3 or K2 のキー押し下げで DSR or CTS が High になります。 ここの回路がうまく動作していません。 SX2 を On すると DSR が High になるはずです。

PC はそれを受けて RTS を制御しないといけません。

とりあえず、次回は

① DTR が High になっている事

② SX2 の On/Off で DSR が High/Low に変化する事

③ PC側のポート設定を確認する

を進める予定です。

この回路図で不思議な点が一つあります。

Switch しているトランジスタのコレクタ負荷抵抗 2.7KΩ が3番端子につながっている事です。 3番は本来 TxD で送信データです。 通信していなければ定常状態、つまり Low になっているはずですが、それを前提にして回路を設計しても良いものやらと感じてしまいます。

外部からの SW 接続で動作 Test をすると Step 1 はOK ですが、Step 2 が正しく動作しません。

そこで回路図を追ってみました。

この回路をみると上側の回路で PC からの RTS 信号で受信動作から送信動作に回路の電源を切り変えています。 ここはテスト的に繋いだ SX1 で On/Off が確認できています。

次に下側の回路で DTR からの信号を電源として、K3 or K2 のキー押し下げで DSR or CTS が High になります。 ここの回路がうまく動作していません。 SX2 を On すると DSR が High になるはずです。

PC はそれを受けて RTS を制御しないといけません。

とりあえず、次回は

① DTR が High になっている事

② SX2 の On/Off で DSR が High/Low に変化する事

③ PC側のポート設定を確認する

を進める予定です。

この回路図で不思議な点が一つあります。

Switch しているトランジスタのコレクタ負荷抵抗 2.7KΩ が3番端子につながっている事です。 3番は本来 TxD で送信データです。 通信していなければ定常状態、つまり Low になっているはずですが、それを前提にして回路を設計しても良いものやらと感じてしまいます。

コメント 0