FPGA で PSK31 (DE0 Nano 編 送信 その5) [Digital Mode]

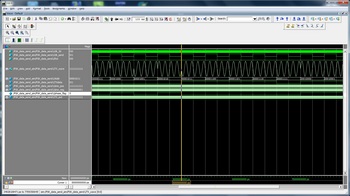

前回はキャリヤが 1kHz、変調信号が 1kHz という条件でしたが、今回はキャリヤが 1kHz、変調信号が 250Hz にしてシミュレーションしてみました。

送信クロックの間に4サイクル分キャリヤが入っています。

データが 0 で反転が繰り返しています。

データが 1 では反転していません。

今は回路検証のために周波数を変えています。

実際には、ここで出来た PSK 信号に帯域制限をかける事になります。

① は、今回のシミュレーションでの構成

② は、sin 0° / 180° をテーブル参照のオフセットとして計算する構成

今後は、汎用性を目指してこの構成を試してみる予定です。

③ は、今までと異なり、送信データをサンプリング周波数までオーバーサンプリングし、それにフィルタで帯域制限をかけ、Zero Cross で得られる 1 / 0 情報で位相を 180° / 0° で変えて乗算し、PSK 出力を得る方法です。

最終的にはこれを作れるように考えます。

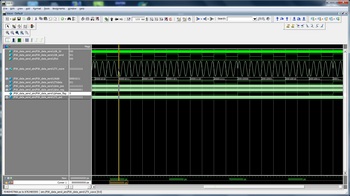

送信クロックの間に4サイクル分キャリヤが入っています。

データが 0 で反転が繰り返しています。

データが 1 では反転していません。

今は回路検証のために周波数を変えています。

実際には、ここで出来た PSK 信号に帯域制限をかける事になります。

① は、今回のシミュレーションでの構成

② は、sin 0° / 180° をテーブル参照のオフセットとして計算する構成

今後は、汎用性を目指してこの構成を試してみる予定です。

③ は、今までと異なり、送信データをサンプリング周波数までオーバーサンプリングし、それにフィルタで帯域制限をかけ、Zero Cross で得られる 1 / 0 情報で位相を 180° / 0° で変えて乗算し、PSK 出力を得る方法です。

最終的にはこれを作れるように考えます。

コメント 0