Verilog の勉強をしています [Simulation]

今、購入した FPGA ボードを使いこなせるように Verilog の勉強をしています。

初めは Trimble Thunderbolt の 1PPS パルス出力を使った周波数カウンタを作ってみるつもりです。

その第一段階として、8桁の同期式 BCD カウンタと 7Seg デコーダー回路を Verilog で書いてシミュレーションしてみました。

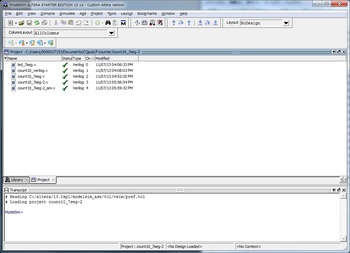

まず、Model-Sim のプロジェクト画面です。

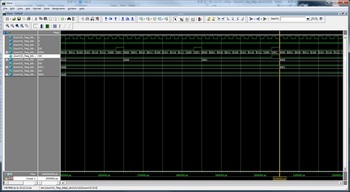

で、シミュレーション結果です。

ちゃんとカウントアップできています。

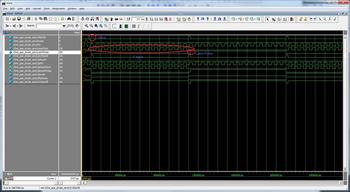

こちらは 1PPS から 1Sec パルスを作り、カウントするパルスを切り出す部分と、表示値のラッチ用パルスを作るところです。 シミュレーションしやすいようにパルス数は適当に減らしています。

このあと、デコーダー部の入力にラッチを追加し、測定結果をシリアル通信で外部に出す回路を追加して、Arduino の LCD 表示シールドにつなげてみようと考えています。

あ~、早く Trimble Thunderbolt のステータス表示スケッチも作らなくては。

先はまだ長いです。

初めは Trimble Thunderbolt の 1PPS パルス出力を使った周波数カウンタを作ってみるつもりです。

その第一段階として、8桁の同期式 BCD カウンタと 7Seg デコーダー回路を Verilog で書いてシミュレーションしてみました。

まず、Model-Sim のプロジェクト画面です。

で、シミュレーション結果です。

ちゃんとカウントアップできています。

こちらは 1PPS から 1Sec パルスを作り、カウントするパルスを切り出す部分と、表示値のラッチ用パルスを作るところです。 シミュレーションしやすいようにパルス数は適当に減らしています。

このあと、デコーダー部の入力にラッチを追加し、測定結果をシリアル通信で外部に出す回路を追加して、Arduino の LCD 表示シールドにつなげてみようと考えています。

あ~、早く Trimble Thunderbolt のステータス表示スケッチも作らなくては。

先はまだ長いです。

Verilog懐かしいです。 習得が早いですね。

by ja1nuh (2013-11-09 19:10)

いえいえ、

ネットでいろいろと書かれている Verilog のプログラムを集めて、それを参考に書いています。

やはり習字と同じで、先生のお手本がないと難しいです。

by ktm (2013-11-10 22:05)

知らない間にコメントに画像認証が付いている。

付けた覚えはないんだけど。

by ktm (2013-11-10 22:06)